Take advantage of the low cost SI simulation offered by Ironwood Electronics, Inc.

Impedance mismatch in contacts in test sockets can affect the signal integrity (SI) performance when testing high-speed semiconductor ICs. This discontinuity is mainly caused by mechanical features in interconnects/contactors that may result in impedance change.

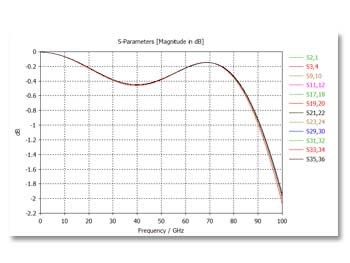

The signal integrity analysis of high-speed electronic designs requires that the interconnect models be valid over a wide bandwidth. By the way of analyzing S-parameters, it is easy to understand the frequency dependent behavior of interconnects /contacts of a test socket. A lot of information is embedded in the S-parameters, and there are many methods to manipulate the S-parameters to reveal the structure’s electromagnetic properties in detail.

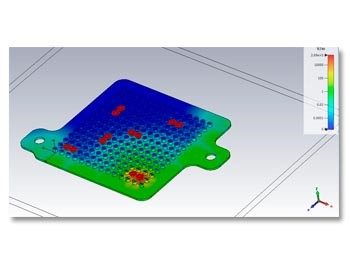

Engineers want ability to correlate the simulation results with measurements in both frequency and time domains. Being able to do so will increase confidence in the design flow, and result in better designs or lower cost. Ironwood Electronics, Inc. offers low cost SI simulation for various interconnects/contactors using CST MWS customized for its customers.